FPGA可靠性设计加固工具(TMR)

概述

深维金刚(ApeAlpha)TMR 工具是北京深维科技有限公司(以下简称“深维科技”)自主研发的现场可编程门阵列(Field-Programmable Gate Array,FPGA)设计加固工具,主要面向航空航天以及高可靠性要求的 FPGA 应用领域,用于为 FPGA 设计提供三模冗余(Triple Modular Redundancy,TMR)加固等一系列的安全保障措施。与同类产品相比,使用方法简单便捷,支持用户自定义加固规则,能够让用户根据自身的应用场景定制化自己独有的加固方案,同时还提供了智能加固引擎,让用户可以根据不同的策略来对设计进行智能加固。

本工具兼容常用设计工具 ISE、Vivado,提供了与现有设计交互的方案,同时原生支持深维科技自主研发的大容量 FPGA 正向设计工具 Dimension。工具在网表层面对设计进行三模加固,避免了 RTL 层加固会被逻辑优化掉的风险。通过使用该工具,用户可以在不改变现有开发流程的情况下,便捷地在网表层面对 FPGA设计引入三模加固。

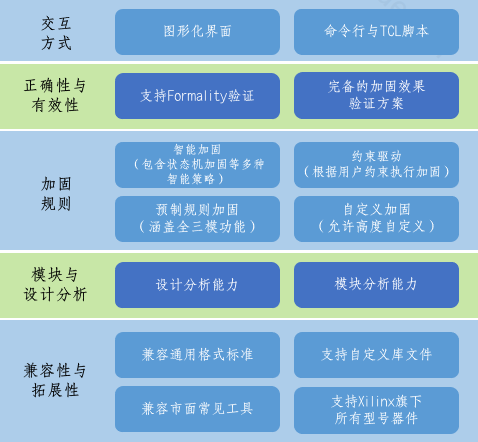

现有功能:

- 器件支持:Virtex7、Kintex7、Artix7 等常用器件;

- 兼容工具:Vivado、ISE、Dimension;

- 功能模块:设计分析、模块分析、模块加固规则配置、TMR 运行;

- 加固规则:资源驱动、预定义规则(通过预定义的规则组合进行便捷加固)、环路加固、智能加固(包含状态机加固等多种智能策略)、全局加固、原语加固规则(按原语类型进行加固)、实例加固规则(提供了高度自定义的能力,按例化元素的名称指定加固规则);

- 交互格式: Verilog 网表、EDIF 网表;

- 验证方案:提供基于形式化验证工具 Formality 的完备的验证策略;

- 操作界面:支持 VS Code 风格的 IDE 环境;

- 运行环境:支持基于 docker 的本地与云端部署。

支持器件:

- 深维金刚 TMR 工具在网表层面对设计进行 TMR 加固,因此只需要提供器件涉及到的原语库,即可实现支持对应的器件。

- 目前深维金刚 TMR 工具整合了 ISE、Vivado 支持的所有原语定义,因此理论上可以支持这两个工具支持的所有器件。